��Ʒ���ࣺӦ��ָ��

��PCIe Express 3.0(PCIe Gen3)����������Ӧ����˵�����˼������ṩ����ͬ����µĸ������ѡ��

���� ��Ȼ���н����(SerDes)ת������ԭ����������ڸ��˼����(PC)�����ϳ���PCIe Gen1/Gen2����Ѷ�ţ���Ҳ�ɼ�Ӧ�õ�ͬ���������Ϊ��������������������Ļ����ӿڡ�������ͭ�µ�ͨ�����Խ�����PCIe Gen3�����ŵ�Ƶ�ʶ�������ӻ�����˳������ͭ�������������������㵼��8Gbit/s PCIe Gen3������Ʒ�Գɱ���Ч�ܡ��ߴ���������Ҫ��

�������˼���Ϊ���ŵ���PCIe Gen3�ӿ��ṩ�dz�����������������������������ӳ����������롢��С�ijߴ硢��������������͵Ĺ��ġ����ߵ�Ч�ܣ��Լ����߾������ijɱ�����Ȼ���� ���˵�PCIe Gen3���������ڳ����ƶ��Σ���������������Ϊ���ɷ����IJ�Ʒ��

�������Ľ�����PCIe Gen3���������Լ���Ŀǰ���ù��˼���Ӧ�õ��ͳɱ�PCIe Gen3����ս������ʹ����PLX�Ͱ�����(Avago)��ͬ�����Ľ������̽��PCIe Gen3��ѧ������Ч�ܡ��ɱ���ģ�����͡��ߴ磬�Լ����������ٵ����⣬�����PCIe Gen3�˶Զ˹�����������Ƽܹ����������˽�������������֧����ҵPCIeӦ�õ�ȫ64Gbit/s(˫��128Gbit/s)ͨѶ������

����PCIe Gen3�������ʷ����ɳ�

�� ��PCIe�������ṩ���봦����(CPU)������ܱߣ����ͼ��ʾ���������ڴ桢�������������ⲿ��������(I/O)���俨�����ӵĸ��ٴ��м���������� Ӣ�ض�(Intel)������Ŀǰ����Ϊ����������������վ���߽������Ļ�������ͬʱҲ����һЩ�ϴ���ϵͳ�г�Ϊ����ʽ���廥���ļ�����

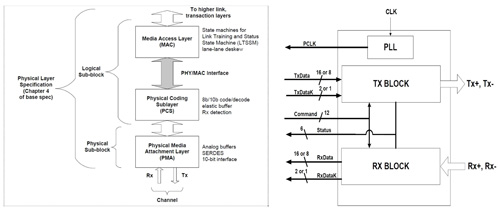

�� ����������(PHY Layer)�ϣ�PCIe�������˵��豸�䵥һ����������ʵ�֣���Ϊͨ��(Lane)��ÿ��ͨ�����������͵�ѹ������ϲѶ�Ŷ���ɣ��γ����������� ���豸��ĸ���ȫ˫��������(Bitstream)����������ʹ��8b/10b���뷽��Ƕ������Ƶ�ʴﵽ�������ݴ����ʡ�Ϊ������ߵ�������PCIe�ŵ� �ɾ�������γɶ����ġ��˼���ʮ���ŵ��Ķ��ŵ������������ŵ����ͷ�����ݡ�

������PCIe Gen1����2003���Ƴ�ʱ��ÿ��ͨ���������ٶȶ���Ϊ2.5Gbit/s�������õ�8b/10b��·���뷨�ή����Ч����20%��PCIe Gen2���ٶȼӱ�Ϊ5Gbit/s�� ������ʮ��ͨ����PCIe������֧�֣��ﵽ�ߴ�160Gbit/s���ܱ����ʡ�ͼ1��ʾΪPCIe Gen1��Gen2�����㹦�ֹܷ���

ͼ1 PCIe Gen1��Gen2�����㹦�ֹܷ�(��)�뷽��ͼ(��) ͼƬ��Դ��Ӣ�ض�

����2010�����PCIe Gen3�������һ�ν��ŵ������ӱ������Գ�Ϊ“��ɢ(Scrambling)”�ļ���ȡ��Gen1��Gen2ʹ�õ�8b/10b��·���뷽ʽ���ɽ����ŵ�����Լ1.5%��

������������PCIe�ӿ���������

��������PCIe�����ĸ�ƵѶ������������迹�ܿ��ŵ�������Ѷ��������������������Խ϶̣���˱Ƚ�������CPU���ܱ�λ�ýӽ������ӡ�

�Ȳ��ۼ����ϵ���ս��ҵ���Ѷ�ʹ�õ�����������������PCIe�����������Ӧ�þ߸߶ȵ���Ȥ�����������������������豸����PCIe����ʱ���������н鴫��ͨѶЭ�������صĵ�������������ɽ���ϵͳ�ӳٲ���ߴ���Ч���⣬ʹ��PCIe���߽�������ϵͳ���Ӷȡ��ɱ����ĵ���ŵ㡣

�� ��Ϊ֧����ЩӦ�ã�ҵ��Ҳ�ƶ��ⲿPCIe(External PCI Express, ePCIe)��ɽ�PCIe Gen1��2.5Gbit/sѶ�Ŵ������쵽�����߳���ͬ����£�Ŀǰ�ѱ�Ӧ���ڰ�������ϵͳ����Ч�������������Լ�������Ҫ�������������ϵͳ������ ��Ʒ������߽�Ӱ��ϵͳ�ȡ�

������Ȼ�����Ѷ�Ż�����������ߵ���˥�����Բο�Ƶ�ʶ�����Ϊ���У��Լ�����Ѷ���������������ƣ���ʵ�ֽ� �������߾��룬ҵ��Ŀǰ�����ePCIe Gen2�����߹����н�������Ŀ���������Щ������PCIe Gen3 8Gbit/s��������ʱ�������Ӹ��ӣ����������ĵȻ���ʱ������������ʵ�ϣ�������PCIe Gen3оƬ������ҵ���з���Ʒʱ��Ҫʹ��Ʒ��߽ϳ������������������������ƽϼѿ��ǣ���ʹ���˳�Ϊ��������PCIe���ߵ�����以����ͭ������� ����

����ֵ��ע����ǣ���PCIe Gen3��ʼ����ʱ���������߽���ͭ�½�������ĵ�����ҳɱ����ͣ���Щ����ʹ���ù��˵�PCIe��ΪĿǰӦ���������������ӷ������������������������� ����������ӿڵ�������������������������������ʹ��PCIe���ɼ����������ͨѶЭ��ת��оƬ�����Ӷ���������ϵͳ�ɱ������ļ�����ͨ���ӳٵ��� �⡣

�������˰�PCIe Gen3���ɷ�������

������ȻPCIe-SIG����ʹ�ù��˵�PCIe Gen3�����輸��ʱ�䣬��Ŀǰ�������ò�Ʒ��Ϊ���ɷ�����ʹ�������Ͽ�ȡ�õ�PCIe Gen3�����ƽ�й��շ���ģ�飬�ɴ�������ض�Ӧ�ù�ѧ������Ʒ�Ŀ������������ȴ�PCIe SIG���Gen2/Gen3���˹����г���

�� ������PCIe��ý����ʿ���(MAC)��PHY��Ľӿڷdz���ӵ�����õ��ļ�˵������˿ɷdz�����ʹ�����������е�PCIe Gen3���������������˵�����ƶ�ƽ�й��շ���ģ�飬����PCIe Gen3����ж���Ķ��ŵ�����SerDes����������PCIe Gen3���ʺϵĸ�Ч��Ӧ�ã��ϱ��յ������Ǽ���������Ҫ���ٰ˸�ƽ���ŵ�������

������ͨ���˵��ʹ��Ŀǰ�����϶�������̵IJ�Ʒʵ�֣��� ��ƽ�йⷢ��/����ģ���еĴ�ֱǻ���淢������(Vertical Cavity Surface Emitting Laser, VCSEL)���顣����VCSEL������ƽ�й�ѧģ���֧�ֶ��ʮ����ƽ���ŵ���ÿ�ŵ���8Gbit/s������ٶ����������ṩ150���ߵ����ߡ�

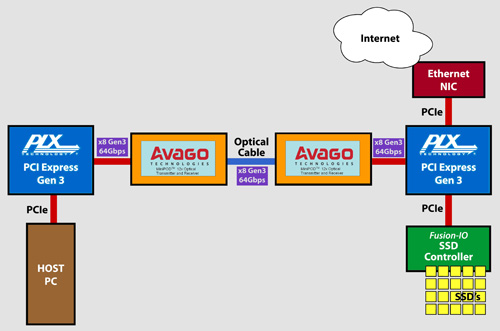

����Ϊ����ʹ�����ò�Ʒ�Ŀ����ԣ����Ľ���һ��������֤չʾϵͳ(ͼ2)�����ں���ʮ��ͨ��PCIe Gen3���������俨�����ؼ������ɣ��������ƶ�ʮ���ŵ�10Gbit/s MiniPOD��ѧģ�飬��ʹ�ð˸���ѧ�ŵ������ĸ���δʹ�á�

��ѧPCIe���������ս��

�������ļܹ�������֤ϵͳ��һ����Ҫ�����ǣ��ṩʹ�������������Ϊ��ѧPCIe����Ӧ�õĿ�����֤�������⣬ԭ��ϵͳ���������Ҳ���ҳ����������������⣬�ر����ڹ�ѧ�����PCIeͨѶЭ��֧���ϣ���Щ���������

����· ���������

����ƽ�й��շ���ģ �鲢δ�ṩ��PCIe��������������������ڵ�50��ķ(Ω)�迹�������档���ʵ��ĸ��ش���ʱ���������ᴥ����������������ն�������ģʽ�������� ����ǣ�������Ϊ��ʼ����һϵ����·̽��Ѷ�ŵĶ��У��Ա��ý��������㲢��Ϊ�Ȼ���·�趨�IJο�����ʹ�ñ�PCIe MAC���֧�ֹ�ѧ������Ӧ���У���������·̽����Ȼ����ܱ��뱻�رա�

����·��������ģʽ

����PCIe�����ӿڰ����������ݴ���ʱ��������ɽ��ܴ���(Electrical IDLE, EIDLE)ģʽ�Ĺ��ܣ�����������������ʱ���ģʽ���ܻ�������⣬ԭ�����շ����ϳ���ů��ʱ����ܻ������·�������ʵ���ƫѹ�����������EIDLE��������EIDLE״̬��

����·Ƶ��

�������ڴֹ�ѧPCIe��������������ͬ���ܼ������˵�����ӣ���˱�����������Dz���ʹ����ͬ�����û�ϵͳƵ��Ѷ�ţ�����ЩӦ�ü���ƪ�����ṩ�ķ����У�������������ʵ��ͬ�����û�Ƶ�ʣ���˶˵�����ܹ�֧���첽Ƶ��������

����· Զ������

�� ���ڴ�Ӧ���У�PCIe������Զ�̹�ѧ���俨������ϵͳǰ���磬���Զ�̵�·��������������ڵ�Դ����ʱ�����Զ����ó����Ա������ض�����ʱ����ȫ ��ʼ������ʼ������������һ��������������ϵͳ����ȫ���û����ƣ���ôϵͳ�������κ�˳����������Ȼ���ַ�ʽ�������������Կ��ƻ�Ӧ��������ϵͳ�ж�ʱ�� ������״̬�dz���Ҫ������������̬�£�������ϵͳȷ����ɴ���������ϵͳ�����������ϵͳ�о����������

����·�ⲿѶ��

�� ��Ŀǰ���ͬ����¶����PCIe�ⲿ���߹���ڹ�ѧ������������صĶ���Ѷ�ţ�����100MHz�����߲ο�Ƶ��(RefClk)������Ҫ��ԭ���� Ƶ�ʿ���PCIe�շ��������ϴ�����ȡ�á��������SB_RTN���˱�Ƶ��Ѷ�ŵĻط�����Ѷ�Žӽš�CPRSNT#��װ������/�´���ϵͳ�ϵ硢 CPWRON�ϴ���ϵͳ��Դ�ȶ�֪ͨ��CWAKE#�����¼��ĵ�Դ����Ѷ�ţ��Լ�CPERST����PERST#����ƽ̨���õȽӽţ���ʹ�ù�������ʱҲ�� ��ʹ�á�

����ѡ��֧�ְ��ŵ���̬���

������������ǰ�Ŀ���������ʵ�����ò�Ʒ��δ�ṩ�Ĺ��ܣ�ͨ����ʹ���ֳ��ɱ��������(FPGA)����ɢ�����ɡ�������PCIe Gen3�������ϣ��г�������ʵ�ָ�����֤ϵͳ���蹦�ܵIJ�Ʒ����Ȼ���Dz�û�������������Ӧ���Ż���

�� ��ѡ�����ʺϵĹ�ѧģ���豾�IJ���Ӧ�÷������������������ǣ������ŵ���������������Եȡ���ȻPCIe������������ġ��ˡ�ʮ����ʮ�����ŵ����� ��ѧģ��ͨ���˻�ʮ����ͨ����̬�ṩ������ѡ���ͨ����̬��ԭ�����侭��ʹ���ڸ�Ч��PCIe 2.0������У�Ԥ��Ҳ����PCIe Gen3���ܵ���ӭ�����⣬�������ŵ�PCIe�˵��ƷҲ������ŶӴ����ḻ�����ѡ�����У�����CXP��MiniPODģ������ȡ�ò�ӵ�����õ� Ч�����ԣ���˳�Ϊ���������������ѡ��

MiniPODģ���е��ƽϼ�

��������ѡ��MiniPOD��ԭ������Ƕ��ʽƽ�й�ѧ��̬��ֱ�Ӱ�װ��ӡˢ��·���ϣ��������õĵ��� ���е��ơ�MiniPOD��ѧģ���ռ�����Ϊ18.6����(mm)×22���ף����ҿɽ���ʮ��ͨ���ı�ƽ����Բ�����ߡ���ƽ���ߵ��ŵ������ȵͼ� ģ��ɽ��ܶ�ջ��Բ���������ṩ���õ��ȹ̶ȼ����ߵ��Ե����ۣ�ͼ3Ϊ����ƽ������ϲ�ʹ��ҵ���MTP������MiniPOD��ѧģ�顣

ͼ3 ʮ���ŵ�Ƕ��ʽƽ�������շ�ģ��MiniPOD

�� ����CXPģ��ʹ�õĵ�·���Ե��װ��ͬ��MiniPOD��ѧģ��ɼ����ڵ�·�����룬���ṩ�������������ӣ�������8Gbit/s����Ѷ�ŵĵ�·�� ���߳��ȼ���5���������ɽ�����ݱ���ЧӦ��ɵĺ�����ʧ���������͡���Ե��װ��������Ĺ�ѧ�����PCIe���߿��ܴﵽ12��20��������������߳� �ȣ��һ�������ĵ�·����ϡ�������ȥǿ�����������Ȼ���Ƶ�����ݻظ�(CDR)�ȼ������Ѷ�����������⡣

�������ķ���ѡ����ʮ���ŵ�PCIe Gen3��������Ϊ�����˵��PCIe��������ԭ���Ǹ������������֧�ֹ�ѧ���������Ĺ��ܣ��˽������ɽ�������⣬��һΪ������ӵ�йر����������Ĺ��ܣ������ѧ�����ṩ50Ω�迹�������ڴ�ģʽ�������������������ݴ�����������ٶ�Э�̡�

����PCIe�������ڶ��������������EIDLE��ԭ���Ǹ�����ܱ��趨Ϊ���Կ���������������״̬�����ݴ����仯���ڴ�ģʽ�£�PCIe�������������ṩ�������ٶ�Э��Ҫ����ض����ݷ��ţ���˹�ѧ�����ܽ����оټ�����������ŵ����ٶ���Ϣ��ͨѶ���ﵽ��ȫ����������

�� ���������ڴ˽����������ĵ�EIDLE���������������������̬��Դ����(Active State Power Management, ASPM)״̬����˻��Ǵ���һ��С���⣬������ʵ���Ͻ������������������������ʼ��������ά���������Խ����Ȼ������������������Դ�������á� BAR��̡��˵�Ŀ���ע�����±�̼�ѶϢ�ڱεȾ�������Ĵ�������

��������������PCIe����������������ǣ�������֧�����ݻظ��õ� �첽Ƶ��ģʽ������PCIe��ѧ�����������ܹ�������������������첽ģʽ����֧����������ӡˢ��·���ϳ���PCIeѶ�����߷����Ÿ��ŵ�ϵͳչƵƵ�� (Spread Spectrum Clocking, SSC)��

���������շ���/���˿�����ʵ�����˰�PCIe

�� ����������ĸ�����֤չʾ�ĵ�·��(ͼ4)�����ڽ���ʮ��ͨ��PCIe Gen3���������俨�����ؼ�������Լ�һ�����佻�����Ĺⷢ�����������ģ���Ӱ壬�ڹ�ѧ��������һ�ˣ���һ���������շ����������ģ��Ľ������ӿڿ� λ�ڵ�·���ϣ������ṩ�����ܱߣ����̬Ӳ����������̫����(Ethernet)HBA����������������ϡ�

ͼ4 ����MiniPODģ������俨

ʵ��������ÿһ�˶�ʹ��PCIe Gen3������оƬ�����նˣ�����Ƶ��/���ݻظ��Լ�ÿ�����ٶ˿ڵķ���/���յȻ������ڽ�����оƬ���շ���ѡ���첽ģʽ����������ڹ�ѧģ���в��������Ƶ�������ݻظ����ɽ�һ������PCIe�ĵ��ӳ����ơ�MiniPOD��ѧģ���ڵ�·������λ�õ���ƣ���·�����߽϶̣�Ҳ���ý�����оƬ��Tx��RxѶ��ֱ�����ѧģ���ӣ����ֻ����������뽻����ϡ�

����ʵ��30��������PCIe Gen3����

�� ��������ʵ����·��ɹ�ʵ����OM3�ĵͳɱ���ģ�����ϣ�ʵ�ֳ���30���ߵ�PCIe Gen3��ͨ�����ߡ������������֧���첽����(��ԭ��SSC�����ṩSSC����)����L0����״̬(�ܿز���ϵͳ�������������������)��PCIe��ͨ �����ٶ�Э����PCIe���������Ȱ��Ź��ܡ�

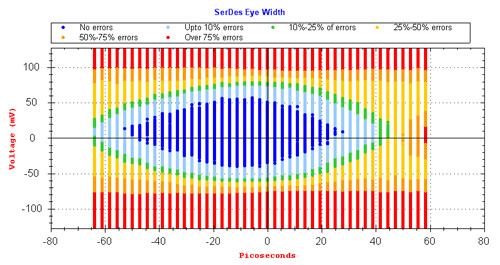

������������ǰ�����۵ļ������⣬��һ��������Ŀǰ�����߱�PCIe��̬��Դ����������ͬ������(��֧�ִ����������)���ܡ���ͼ5��ͼ��˵������������30��������ʱ��ӵ�����õ�Ѷ�������Լ���������ݻظ���

ͼ5 PCIe Gen3��������30���߹������ݴ�����ͼ

�� ���ڱ���ʵ�������У�MiniPOD��ѧģ���֧��PCIe Gen3��ÿ�ŵ�8.0Gbit/s���ٶ���������ʵ���Ͽ�֧��1G?10.3125 Gbit/s�Ŀ��㴫�����ʣ������Щ��ѧ�������5.0Gbit/s��PCIe Gen2��2.5Gbit/s��PCIe Gen1���������������̬Ҳ��������Ч�ܡ���һ�������ʷ�Χ�������ù���ʦ����ʵ��PCIe Gen3�����������ӣ�Ҳ����Ϊδ���ض�Ӧ�ò�Ʒ�������ʹ�ѧ���������ݵĻ�����